The current push for domestic semiconductor self-sufficiency in the United States faces a structural failure point: the geographical decoupling of front-end wafer fabrication from back-end advanced packaging. While multi-billion dollar subsidies focus on "leading-edge" nodes—the printing of transistors onto silicon—they largely ignore the reality that a finished chip cannot function until it undergoes Assembly, Testing, and Packaging (ATP). Currently, even if a chip is designed in California and fabricated in Arizona, it must travel roughly 7,000 miles to Taiwan or Malaysia to be finalized. This creates a logistics-induced latency and a geopolitical single point of failure that renders the concept of "onshore production" a misnomer.

The Architecture of the Packaging Bottleneck

To understand why the "round trip" exists, one must define the evolution of the chip itself. In the previous era of Moore’s Law, performance gains came from shrinking transistors. In the current era, gains are driven by Heterogeneous Integration. Instead of one giant piece of silicon, engineers combine multiple smaller "chiplets" into a single package. This transition shifts the value density from the wafer to the package.

The bottleneck is defined by three distinct technical constraints:

- Interconnect Density: Traditional wire-bonding or "flip-chip" methods lack the bandwidth required for AI workloads. Advanced techniques like Chip on Wafer on Substrate (CoWoS) require sub-micron precision that is currently concentrated within a handful of facilities in Taiwan.

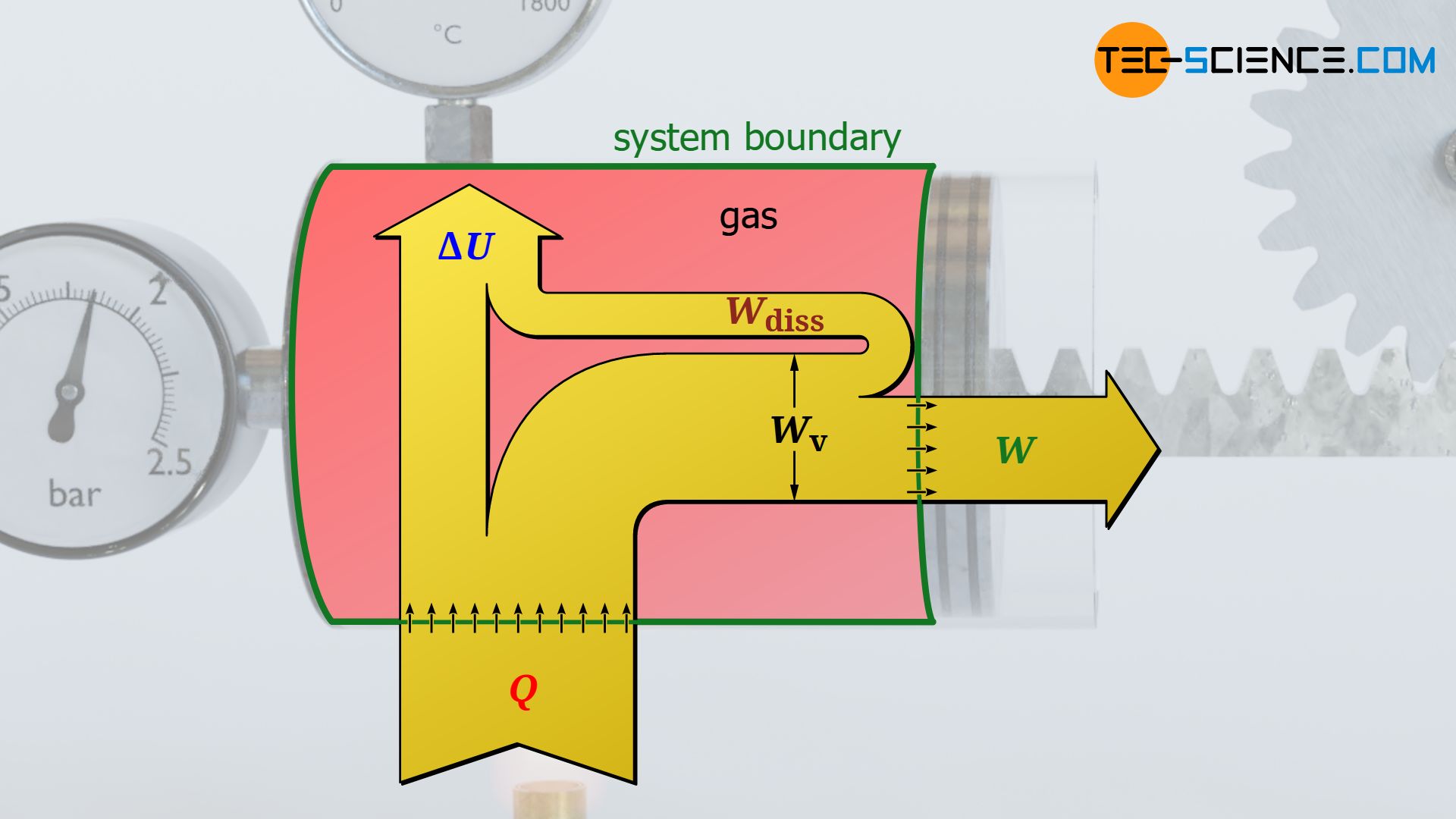

- Thermal Dissipation Limits: As power density increases, the package acts as the primary heat management system. The materials science required to prevent silicon from melting under load is as complex as the lithography used to create it.

- The Substrate Gap: The high-end organic substrates (ABF substrates) required for these chips are produced almost exclusively in Asia. Without a domestic substrate supply chain, a U.S.-based packaging plant remains an island without a bridge.

The Cost Function of Geographic Dispersal

The economic rationale for shipping chips across the Pacific for assembly is rooted in a historical cost-optimization model that is now colliding with national security imperatives. Analysts often mistake labor costs as the primary driver; in reality, the driver is ecosystem inertia.

The total cost of a semiconductor is a function of yield, cycle time, and capital utilization:

$$C_{total} = \frac{C_{wafer} + C_{packaging}}{Y_{total}} + L_{logistics}$$

Where:

- $C_{wafer}$ is the front-end cost.

- $C_{packaging}$ is the back-end cost.

- $Y_{total}$ is the cumulative yield (the product of fabrication yield and packaging yield).

- $L_{logistics}$ represents the risk-adjusted cost of transport and inventory holding.

In the U.S., $C_{packaging}$ is significantly higher not because of wages, but because of the lack of a "circular" ecosystem. In Taiwan, a packaging facility sits within a 30-mile radius of the fabrication plant, the substrate manufacturer, and the testing house. This proximity allows for rapid iteration when yields drop. In a trans-pacific model, a yield excursion (a sudden spike in defects) can take weeks to identify and remediate, resulting in millions of dollars in scrapped silicon.

The CoWoS Monopoly and Logic-Memory Proximity

High-performance AI accelerators, such as those produced by NVIDIA or AMD, rely on a specific architecture where High Bandwidth Memory (HBM) is placed immediately adjacent to the logic die. This connection occurs via a silicon interposer—a bridge with thousands of connections per square millimeter.

The technical dominance of TSMC’s CoWoS (Chip on Wafer on Substrate) process creates a gravitational pull toward Taiwan. If a chip is fabricated at a TSMC "Gigafab" in Tainan, it is logistically and technically optimal to move it to a CoWoS line nearby. Attempting to ship these unfinished wafers to a third-party OSAT (Outsourced Semiconductor Assembly and Test) provider in the U.S. introduces handling risks and proprietary interface hurdles.

The U.S. currently possesses roughly 3% of global packaging capacity, and almost none of that is "advanced" in the sense of supporting HBM integration at scale. This creates a strategic contradiction: the U.S. is subsidizing the most advanced "brains" (logic) while remaining dependent on foreign "bodies" (packaging) to make those brains functional.

Vertical Integration as a Geopolitical Defensive Strategy

For the U.S. to break the round-trip cycle, the strategy must shift from subsidizing individual factories to subsidizing "Process Flows." A standalone packaging plant in the U.S. will fail if it has to import every substrate and ship every finished chip back to Asia for final system integration.

The path to domestic autonomy requires three structural shifts:

1. Standardization of Chiplet Interconnects

Currently, advanced packaging is often proprietary. If Intel, TSMC, and Samsung all use different "glue" to connect their chiplets, the packaging layer becomes a silo. Adopting open standards like UCIe (Universal Chiplet Interconnect Express) would allow a domestic packaging ecosystem to service multiple designers, increasing the "utilization" variable in the cost equation.

2. Redefining "Fabless" Models

The traditional fabless model (where a company only designs the chip) is becoming obsolete. Leading designers must now be "Package-Aware." This means designing the silicon with the specific constraints of the packaging facility in mind. If the U.S. wants to lead in AI, its design firms must co-invest in local packaging R&D to ensure their next-generation architectures can actually be built on-shore.

3. Substrate Sovereignty

The "unsexy" part of the supply chain—the Ajinomoto Build-up Film (ABF) and the high-density build-up substrates—is the weakest link. These components are thin, high-precision layers of resin and copper. Without domestic production of these materials, the packaging plant is merely an assembly line for foreign-sourced components.

The Risks of Half-Measures

Investing in front-end fabrication (CHIPS Act Phase 1) without a commensurate, massive investment in the back-end (CHIPS Act Phase 2) results in a "Fortress on an Island" scenario. The U.S. would have the capability to print the world's most advanced circuits but would be unable to turn them into a product without permission from the logistics networks of the South China Sea.

The risk is not just a supply chain disruption, but a "know-how" atrophy. As packaging becomes the primary driver of performance gains (the "More than Moore" era), the intellectual property of the semiconductor industry is migrating from the transistor to the interconnect. If that IP remains concentrated in one geographic region, the U.S. remains a secondary player in the value chain, regardless of how many lithography machines are located in Arizona or Ohio.

The strategic play is the creation of "Mega-Campuses" that colocate fabrication, advanced packaging, and substrate manufacturing. This eliminates the "round trip" entirely, reducing cycle times by an estimated 25% and removing the geopolitical vulnerability of the Pacific transit. Anything less is merely shifting the location of the bottleneck, rather than removing it. Firms must prioritize "time-to-market" over "cost-per-unit" to justify this shift, treating supply chain resilience as a performance metric equivalent to clock speed or power efficiency.